Provided for non-commercial research and education use. Not for reproduction, distribution or commercial use.

This article appeared in a journal published by Elsevier. The attached copy is furnished to the author for internal non-commercial research and education use, including for instruction at the authors institution and sharing with colleagues.

Other uses, including reproduction and distribution, or selling or licensing copies, or posting to personal, institutional or third party websites are prohibited.

In most cases authors are permitted to post their version of the article (e.g. in Word or Tex form) to their personal website or institutional repository. Authors requiring further information regarding Elsevier's archiving and manuscript policies are encouraged to visit:

http://www.elsevier.com/copyright

Thin Solid Films 518 (2010) 6325-6329

Contents lists available at ScienceDirect

Thin Solid Films

journal homepage: www.elsevier.com/locate/tsf

# thinged films

# The effect of annealing on amorphous indium gallium zinc oxide thin film transistors

Hyeon-seok Bae<sup>a</sup>, Jae-Hong Kwon<sup>a</sup>, Seongpil Chang<sup>a</sup>, Myung-Ho Chung<sup>a</sup>, Tae-Yeon Oh<sup>a</sup>, Jung-Ho Park<sup>a</sup>, Sang Yeol Lee<sup>b</sup>, James Jungho Pak<sup>a</sup>, Byeong-Kwon Ju<sup>c,\*</sup>

<sup>a</sup> Display and Nanosystem Laboratory, College of Engineering, Korea University, Republic of Korea

<sup>b</sup> Electronic Materials Center, Korea Institute of Science and Technology, Republic of Korea

<sup>c</sup> School of Electrical Engineering, College of Engineering, Korea University, Republic of Korea

### ARTICLE INFO

Available online 25 March 2010

Keywords: Oxide thin film transistor Amorphous indium gallium zinc oxide Rapid thermal annealing Contact resistance Transmission line method (TLM)

# ABSTRACT

This paper presents the post-annealing effects, caused by rapid thermal annealing (RTA), on amorphous indium gallium zinc oxide (a-IGZO) thin film transistor's (TFT) electrical characteristics, and its contact resistance ( $R_c$ ) with thermally grown SiO<sub>2</sub> gate dielectric on silicon wafer substrates. The electrical characteristics of two types of TFTs, one post-annealed and the other not, are compared, and a simple model of the source and drain contacts is applied to estimate the  $R_c$  by a transmission line method (TLM). Consequently, it has been found that the post-annealing does improve the TFT performances; in other words, the saturation mobility ( $\mu_{sat}$ ), the on/off current ratio ( $I_{ON/OFF}$ ), and the drain current ( $I_D$ ) all increase, and the  $R_c$  and the threshold voltage ( $V_T$ ) both decrease. As-fabricated TFTs have the following electrical characteristics; a saturation mobility ( $\mu_{sat}$ ) as large as 0.027 cm<sup>2</sup>/V s,  $I_{ON/OFF}$  of 10<sup>3</sup>, sub-threshold swing (SS) of 0.49 V/decade,  $V_T$  of 32.51 V, and  $R_c$  of 969 MΩ, and the annealed TFTs have improved electrical characteristics as follows; a  $\mu_{sat}$  of 3.51 cm<sup>2</sup>/V s,  $I_{ON/OFF}$  of 10<sup>5</sup>, SS of 0.57 V/decade,  $V_T$  of 27.2 V, and  $R_c$  of 847 kΩ.

© 2010 Elsevier B.V. All rights reserved.

# 1. Introduction

Currently, flexible and transparent electronic devices are the most promising field to realize the future-oriented technologies such as flexible display, solar cells, touch panel and wearable computings [1]. Thus, transparent thin film transistors (TFTs) are one of the key devices for achieving these products and these TFTs have been fabricated using oxide materials as active layers and transparent conducting oxides (TCOs) [2]. Until now, several binary, ternary, and guaternary oxide semiconductors have been selected and tested in recent years [3]. Among them, the amorphous indium gallium zinc oxide (a-IGZO), which is one of the most attractive materials, has been found to be appropriate for use as an active channel of TFTs because of its excellent electrical and optical characteristics [4–9]. The a-IGZO film has a wide bandgap and high transparency in the visible region as well as being able to be fabricated at low temperatures [10]. Because the ns-orbital of metal cation is larger than the 2p-orbital of oxygen anion, the a-IGZO shows high mobility even though it has amorphous structure. In the case of fabricating TFTs on glass or plastic substrates, the process temperature is more important for manufacturing devices; accordingly, the a-IGZO has great potential to replace the existing silicon based semiconductors, such

as polycrystalline and amorphous silicon, and organic based semiconductors, as an active layer of the TFT backplane of the flat panels and future generation displays [11–13]. Since Hosono et al. reported the fabrication of high performance a-IGZO based TFTs many researchers have also reported fruitful achievements in a-IGZO based TFTs [14,15]. Finally, these a-IGZO TFTs have shown excellent performances for realizing future displays, such as those demanding high mobility (>10 cm<sup>2</sup>/V s), having flexible properties, and possessing transparency in the visible range [16]. In fabrication of a-IGZO based TFTs, the a-IGZO has been deposited by using radio frequency (rf) magnetron sputtering as an active channel. This technique generally provides such benefits as high deposition rates and has low processing temperatures [17]. However, in spite of these merits, the rf magnetron sputtering method occasionally results in lower TFT performances due to the increase in the surface morphology roughness. Because of the interface charge trap, scattering, and the contact resistance  $(R_C)$ , a rough surface results in a decrease in the TFT's saturation mobility ( $\mu_{sat}$ ), the on/off current ratio, and the on drain current, as well as increasing the threshold voltage. To overcome these problems, the RTA is a very useful technique with many advantages, such as the short annealing time, and prevention of any strains or reactions at the film-substrate interface [18]. In this work, a-IGZO TFTs are prepared on a SiO<sub>2</sub>/p-Si substrate. And then, in order to decrease the  $R_{C}$ , the RTA is performed on the device. Finally, the two devices are compared and analyzed: (a) a-IGZO TFT and (b) RTA treated a-IGZO TFT. By using these processes, a-IGZO based TFTs are fabricated on a SiO<sub>2</sub> gate dielectric, which has excellent performance.

<sup>\*</sup> Corresponding author. Tel.: +82 2 3290 3237; fax: +82 2 3290 3791. *E-mail address:* bkju@korea.ac.kr (B.-K. Ju).

<sup>0040-6090/\$ –</sup> see front matter 0 2010 Elsevier B.V. All rights reserved. doi:10.1016/j.tsf.2010.02.073

H. Bae et al. / Thin Solid Films 518 (2010) 6325-6329

#### 2. Experimental details

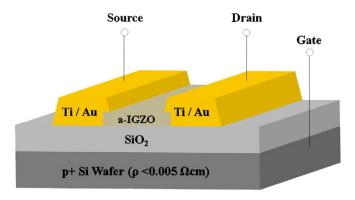

Fig. 1 shows a schematic cross section view of the TFT, which has been fabricated using phosphorous doped p-type silicon wafer with very low resistivity ( $\rho$ <0.005  $\Omega$  cm). The *p*-type Si wafer with low resistivity is used as the gate electrode. A 100-nm-thick SiO<sub>2</sub> layer is thermally grown on substrates by using a furnace (>1100 °C). These substrates are cleaned by acetone, methanol, and de-ionized water in an ultrasonic bath. As the active layer, an a-IGZO thin film of 50 nm is deposited using rf magnetron sputter at room temperature. The initial vacuum level is lower than  $1 \times 10^{-6}$  Torr and the working pressure and rf-power are maintained at 5 mTorr and 100 W, respectively during the sputtering. Before sputtering, pre-sputtering is performed to remove any contamination on the target surface, for 5 min. The active layer is patterned by conventional photolithography and a wetetching process. Then, as the source/drain (S/D) electrodes, Ti of 10 nm and Au of 90 nm are deposited by e-beam and thermal evaporation, at room temperature. In this process, the basal vacuum is lower than  $1 \times 10^{-5}$  Torr, and the thickness is controlled by quartz thickness monitor. The S/D electrodes are patterned by conventional photolithography and a lift-off process. The channel width is designed to be 50  $\mu$ m, and the channel length is varied from 2  $\mu$ m to 200  $\mu$ m. In this work, two devices have been fabricated: (a) an a-IGZO TFT without post-annealing, and (b) an a-IGZO TFT with post-annealing. The post-annealing process is performed in nitrogen atmosphere by using rapid thermal annealing equipment at 200 °C for 1 min. Also electrical characteristics of devices are measured by a semiconductor parameter analyzer (Keithley SCS 4200). Structural analysis and surface analysis have been performed by using atomic force microscopy (AFM, XE-100 system) and X-ray diffraction (XRD, Rigako D/MAX2200). Furthermore, the  $R_{\rm C}$  is analyzed by the transmission line method (TLM).

## 3. Results and discussions

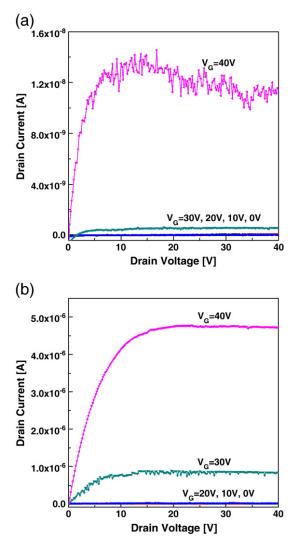

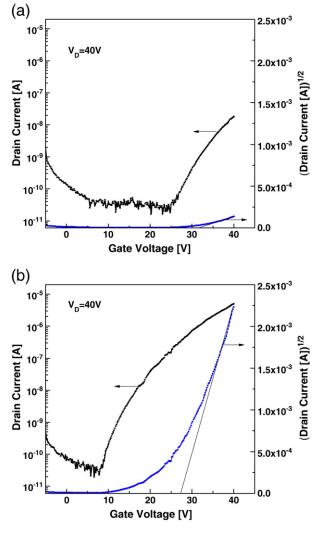

Figs. 2 and 3 show the electrical characteristics, expressed by plotting output and transfer curves for the two types of TFT devices, one with RTA and the other without. These TFTs have a 50  $\mu$ m channel width and a 100  $\mu$ m channel length. As shown in Fig. 2, both devices present the operation of a typical *n*-channel enhancement mode TFT [6]. A hard saturation is only seen in the output curve of annealed TFT. Fig. 3(a) and (b) shows the transfer characteristics of the as-fabricated and post-annealed TFTs, respectively. It is observed that a-IGZO TFT without RTA has a more unstable wide off-level range, and a higher threshold voltage (*V*<sub>T</sub>) than the TFT with RTA. It is clearly seen that annealing one's characteristic is more suitable for TFT as a switching device, than another because of the resulting efficiency and stability. Table 1 shows a comparative list of the electrical characteristics of a-IGZO TFTs with and without post-annealing process. The *V*<sub>T</sub> and  $\mu_{sat}$

Fig. 1. Schematic cross section of the a-IGZO based TFT with  ${\rm SiO}_2$  gate dielectric on silicon substrates.

Fig. 2. Output characteristics of the a-IGZO based TFTs (a) with and (b) without post-RTA.

are estimated by linearly fitting the square root of the drain-source current ( $I_{DS}$ ) versus the gate-source voltage ( $V_{GS}$ ) curve in the saturation region. The following equation is the expression for the operation of a field effect transistor in the saturation region [19]:

$$I_{\rm DS} = \left(\frac{C_{\rm i}\mu_{\rm sat}W}{2L}\right) \left(V_{\rm GS} - V_{\rm T}\right)^2 \text{ for } \left(V_{\rm DS} > V_{\rm GS} - V_{\rm T}\right) \tag{1}$$

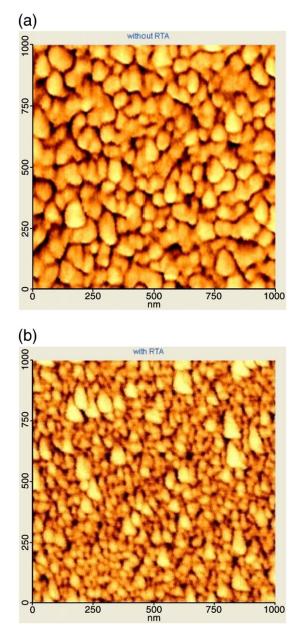

where *W* is the channel width, *L* is the channel length, and  $C_i$  is the capacitance per unit area of the gate insulator (around 34.5 nF/cm<sup>2</sup> for SiO<sub>2</sub> gate dielectrics). This result, caused by the RTA from a rearrangement of the surface morphology, leads to a much improved interface condition between the active layer and the electrodes [20]. Thus, good interfacial condition brings improved electrical performances of a-IGZO TFTs, giving a higher on current and lower V<sub>T</sub>, which is important in achieving a low voltage driven device. If the a-IGZO active channel has poor surface roughness, then this leads to valleys in the channel region, which may act as carrier traps with a number of scatterings [21]. Fig. 4(a) and (b) shows the AFM image of the TFT active channel, with and without RTA, respectively. The RTA effect is also recognized by using the AFM image which reveals the active channel surface morphology difference in each type of TFT. The TFT without RTA has a surface uniformity with a root mean square value (RMS) of roughness of 2.209 nm. On the other hand, the TFT with RTA has a RMS roughness of 1.270 nm. As mentioned previously, the RMS

H. Bae et al. / Thin Solid Films 518 (2010) 6325-6329

Fig. 3. Transfer characteristics of the a-IGZO based TFTs (a) without and (b) with post-RTA.

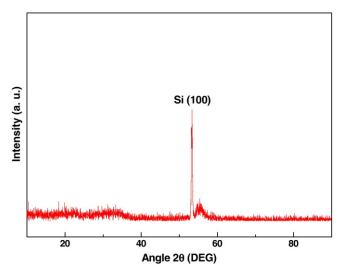

roughness value of the RTA treated TFT is lower than the value of the TFT without RTA. This means that the RTA treatment ensures a smoother active channel surface morphology. The smooth surface morphologies of the a-IGZO thin films can develop good interfaces for both the source and the drain electrode contact regions with the active channel [22]. If the a-IGZO thin film can be crystallized by RTA, the surface roughness will be increased owing to the formed grains. However, the reduced surface roughness means a non-crystallized a-IGZO thin film, and it is confirmed that the a-IGZO thin film maintains an amorphous phase, as shown in Fig. 5. The XRD patterns of the annealed a-IGZO films have only one peak, monopolized at 53°, which matches that of the p+ silicon. As a result, a-IGZO film's crystallinity is not influenced by RTA. The concentration of as-fabricated a-IGZO and

Table 1

List of electrical characteristics of TFT, comparing the RTA process.

|                         | Saturation<br>mobility (µ <sub>sat</sub> )<br>[cm²/V s] | On/off<br>current ratio<br>(I <sub>ON/OFF</sub> ) | Subthreshold<br>swing (V <sub>SS</sub> )<br>[V/decade] | Threshold<br>voltage (V <sub>T</sub> )<br>[V] |

|-------------------------|---------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------|-----------------------------------------------|

| IGZO TFT<br>Without RTA | $2.71 \times 10^{-2}$                                   | $1.13\!\times\!10^3$                              | $4.92 \times 10^{-1}$                                  | 32.51                                         |

| IGZO TFT<br>With RTA    | 3.51                                                    | $1.89 \times 10^{5}$                              | $5.73 \times 10^{-1}$                                  | 27.27                                         |

Fig. 4. AFM images of the IGZO film on the  $SiO_2$  gate dielectric (a) without and (b) with post-RTA.

RTA treated thin films is estimated to be about  $1.0 \times 10^{18}$  cm<sup>-3</sup> and  $8.4 \times 10^{17}$  cm<sup>-3</sup>, respectively. Also, following is expression for the estimation of carrier concentration [24].

$$N_{\rm CH} = \frac{(V_{\rm on}C_{\rm i})}{qt_{\rm CH}} \left[ \rm cm^{-3} \right]$$

<sup>(2)</sup>

where *q* is the unit charge quantity, and  $t_{CH}$  is the thickness of active layer. The carrier concentration within a-IGZO thin film is almost not changed by RTA treatment. So, the change of carrier concentration is negligible in terms of thin film characteristics. In case of a-IGZO thin film, thermal energy is required to rearrange atoms on the local sites. In other words, annealing temperature is attributed to internal modifications in the semiconductor structure leading to improved local atomic rearrangement [23]. However, annealing temperature of 200 °C is not enough to fully rearrange atoms in a-IGZO thin film. This is because all devices have been exposed to temperature of about 150 °C while sputtering is performed. Therefore, the reduction of contact resistance is

H. Bae et al. / Thin Solid Films 518 (2010) 6325-6329

Fig. 5. X-ray diffraction patterns of the as-deposited a-IGZO thin film and after annealing at 200 °C on *p*-type silicon wafer.

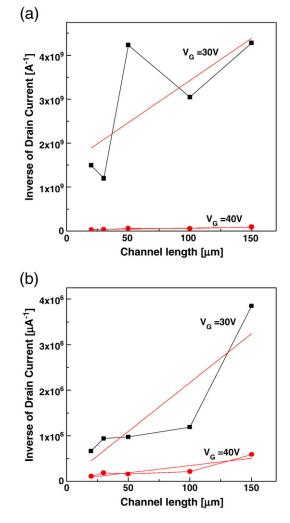

a dominant factor to improve the device performance in this work. Finally, to verify annealing effects that make surface morphology smoother and improve TFT performance, we suppose that surface morphology makes contact resistance low. Thus, we calculate contact resistance by using TLM technique. To obtain the R<sub>C</sub> of the active channel and electrodes, a simplified TFT structure is designed to a variety of channel lengths, ranging from 20 µm to 150 µm, and the resulting drain current measured for each case. Fig. 6(a) and (b) shows the inverse of the drain current as a function of the channel length for each TFT. It was assumed that as the source and drain contacts resistance is separated from the potential drop across the contacts, the contact resistance can be calculated by plotting the inverse of drain current versus channel length, extrapolating the y-axis intercept (where the channel resistance disappears), and multiplying by the drain-source voltage [25]. The resistance values for  $V_{\rm G} = 40$  V are approximately 847 k $\Omega$  with RTA, and 969 M $\Omega$  without RTA. (The total  $R_c$  is the sum of the source and drain  $R_c$ with the active layer). As a result, the RTA makes the surface roughness decreased that caused the R<sub>C</sub> to decrease. Therefore, the TFT's electrical characteristics, such as the  $\mu_{sat}$ , the on/off current ratio, and the  $V_{T}$ , are improved [20].

# 4. Conclusions

In this study, the electrical characteristics of two types of TFT, with and without RTA, are presented by plotting the output and transfer curves. By comparing these TFTs, the post-annealed TFT is found to be more suitable to be used for switching devices, and has better performances, such as higher  $\mu_{\rm sat}$ , larger currents and on/off ratios, as well as lower  $V_{\rm T}$ , than others. The  $R_{\rm C}$  has been analyzed by the TLM technique, and it has been found that the RTA leads to decreased  $R_{\rm C}$ , thereby leading to improvement of the electrical characteristics of the TFT. In consequence, the RTA effect on a-IGZO TFT's electrical characteristics has been presented. Future work plans to fabricate a-IGZO TFTs on the plastic substrates. It is expected that this work will be useful in further advancing the oxide based TFT technology for future devices.

#### Acknowledgements

This work was supported by the IT R&D program of MKE/KEIT [KI002182, TFT backplane technology for next generation display].

Fig. 6. Inversion of drain current as a function of the channel length for TFT (a) without and (b) with post-RTA.

#### References

- [1] J.F. Wager, Science 300 (2003) 1245.

- [2] P. Görrn, M. Sander, J. Meyer, M. Kröger, E. Becker, H.H. Johannes, W. Kowalsky, T. Riedl, Adv. Mater. 18 (2006) 738.

- Y. Sun, J.A. Rogers, Adv. Mater. 19 (2007) 1897. [3]

- [4] J.H. Kim, B.D. Ahn, C.H. Lee, K.A. Jeon, H.S. Kang, S.Y. Lee, Thin Solid Films 516 (2008) 1529.

- [5] M. Kim, J.H. Jeong, H.J. Lee, T.K. Ahn, H.S. Shin, J.S. Park, J.K. Jeong, Y.G. Mo, H.D. Kim, Appl. Phys. Lett. 90 (2007) 212114.

- R.L. Hoffman, B.J. Norris, J.F. Wager, Appl. Phys. Lett. 82 (2003) 733.

- N.L. Dehuff, E.S. Kettenring, D. Hong, H.Q. Chiang, J.F. Wager, R.L. Hoffman, C.-H. [7] Park, D.A. Keszler, J. Appl. Phys. 97 (2005) 064505

- [8] H.Q. Chiang, J.F. Wager, R.L. Hoffman, J. Jeong, D.A. Keszler, Appl. Phys. Lett. 86 (2005) 013503.

- [9] Dhananjay, C.-W. Chu, Appl. Phys. Lett. 91 (2007) 132111.

- [10] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, H. Hosono, Nature (Lond) 432 (2004) 488.

- [11] J.-I. Song, J.-S. Park, H. Kim, Y.-W. Heo, J.-H. Lee, J.-J. Kim, G.M. Kim, B.D. Choi, Appl. Phys. Lett. 90 (2007) 022106.

- [12] J.K. Jeong, J.H. Jeong, H.W. Yang, J.S. Park, Y.G. Mo, H.D. Kim, Appl. Phys. Lett. 91 (2007) 113505.

- J.S. Park, J.K. Jeong, Y.G. Mo, H.D. Kim, Appl. Phys. Lett. 90 (2007) 262106. [13]

- A. Tsukazaki, A. Ohtomo, T. Onuma, M. Ohtani, T. Makino, M. Sumiya, K. Ohtani, [14] S.F. Chichibu, S. Fuke, Y. Segawa, H. Hosono, H. Koinuma, M. Kawasaki, Nat. Mater. 4 (2005) 42.

- [15] H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, K. Nomura, T. Kamiya, H. Hosono, Appl. Phys. Lett. 89 (2006) 112123.

- [16] H.D. Kim, J.K. Jeong, Y.-G. Mo, H.K. Chung, Proc. Int. Meet. Inf. Display 8 (2008) 119.

[17] S. Lin, Y. Chen, C. Wang, K. Kao, C. Chan, J. Electr. Mater. 38 (2009) 453.

[18] R.P.S. Thakur, R. Singh, Appl. Phys. Lett. 64 (1994) 327.

- [19] C.R. Kagan, P. Andry, Thin-film Transistors, Marcel Dekker, New York, 2003.

H. Bae et al. / Thin Solid Films 518 (2010) 6325-6329

- [20] Q. Feng, L.M. Li, Y. Hao, J.Y. Ni, J.C. Jhang, Solid State Electron. 53 (2009) 955.

[21] D.K. Hwang, W. Choi, J.-M. Choi, K. Lee, J.H. Park, E. Kim, J.H. Kim, S. Im, J. Electrochem. Soc. 154 (2007) H933.

[22] J. Kwon, J. Seo, S. Shin, B.K. Ju, J. Phys. D: Appl. Phys. 42 (2009) 065105.

[23] E.M.C. Fortunato, LM.N. Pereira, P.M.C. Barquinha, A.M. Botelho do Rego, G. C. Charlen, Charlen March 2010 (2010) 202100.

- Gonçalves, A. Vilà, J.R. Morante, R.F.P. Martins, Appl. Phys. Lett. 92 (2008) 222103.

- [24] J.S. Park, J.K. Jeong, H.J. Chung, Y.G. Mo, H.D. Kim, Appl. Phys. Lett. 92 (2008) 072104.

- [25] H. Klauk, G. Schmid, W. Radlik, W. Weber, L. Zhou, C.D. Sheraw, J.A. Nichols, T.N. Jackson, Solid State Electron. 47 (2003) 297.